Structures and Unions in SV

Structure in systemverilog, significance of typedef in structures, structure example without typedef, structure example with typedef, types of structures, packed structures, packed structure example, unpacked structures, passing a structure in function or task, syntax for packed signed structure, unions in systemverilog, union example.

Stack Exchange Network

Stack Exchange network consists of 183 Q&A communities including Stack Overflow , the largest, most trusted online community for developers to learn, share their knowledge, and build their careers.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

systemverilog structure initialization with default = '1

Can someone shed light on what this SystemVerilog code should do:

Is this legal? I can't quite figure out the spec well enough to tell. This doesn't work right with Vivado, and I'm not sure why.

This works:

Thanks, Nachum

- system-verilog

2 Answers 2

Yes, it is legal SystemVerilog. Refer to IEEE Std 1800-2012 § 10.9 Assignment patterns

my_struct s = '{default:'1, c:0}; is equivalent to my_struct s = '{a:16'hFFFF, b:16'hFFFF, c:16'h0000}; my_struct s = '{default:0, c:'1}; is equivalent to my_struct s = '{a:16'h0000, b:16'h0000, c:16'hFFFF};

Your version Vivado might not have implemented the default:'1 feature yet or it could be a bug in the simulator. Try to run the latest version.

Try default:16'hFFFF or default:-1 as possible work around.

One way to define complex structs can be explained with an example.

Lets be the following struct, which is a struct of integer arrays and a sub-struct called: AXI_PRM_STRCT

That complex struct can be initialized with literals in the following way:

There is other ways to init with literals

- \$\begingroup\$ The example is very nice, but where is the {default:'1} that was asked about? \$\endgroup\$ – G Eitan Commented Jun 10, 2022 at 6:47

Your Answer

Sign up or log in, post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged hdl system-verilog vivado or ask your own question .

- The Overflow Blog

- How to build open source apps in a highly regulated industry

- Community Products Roadmap Update, July 2024

- Featured on Meta

- We spent a sprint addressing your requests — here’s how it went

- Upcoming initiatives on Stack Overflow and across the Stack Exchange network...

Hot Network Questions

- Times of a hidden order

- What does a letter "R" means in a helipad?

- Dagesh on final letter kaf

- Imagining Graham's number in your head collapses your head to a Black hole

- Position where last x halfmoves are determined

- Is there any other reason to stockpile minerals aside preparing for war?

- What’s the highest salary the greedy king can arrange for himself?

- Line from Song KÄMPFERHERZ

- What are these courtesy names and given names? - confusion in translation

- Geometry question about a six-pack of beer

- Can you help me to identify the aircraft in a 1920s photograph?

- Sitting on a desk or at a desk? What's the diffrence?

- Hölder continuity in time of heat semigroup

- Are there examples of triple entendres in English?

- How can we describe intellect in a way that relates to philosophical knowledge?

- Use of Compile[] to optimize the code to run faster

- How do guitarists remember what note each string represents when fretting?

- Do Christians believe that Jews and Muslims go to hell?

- A very basic autosegmental tree using forest

- Help identifying hollow spring / inverted header sockets

- How well does the following argument work as a counter towards unfalsifiable supernatural claims?

- How much time do I need on my Passport expiry date to leave Australia for South Africa?

- Is it unfair to retroactively excuse a student for absences?

- Is there any legal justification for content on the web without an explicit licence being freeware?

SystemVerilog Packed Arrays

There are two types of arrays in SystemVerilog - packed and unpacked arrays.

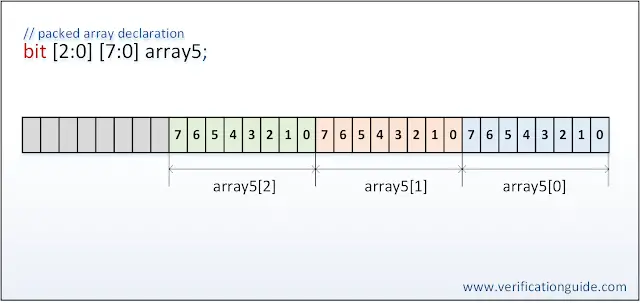

A packed array is used to refer to dimensions declared before the variable name.

A packed array is guaranteed to be represented as a contiguous set of bits. They can be made of only the single bit data types like bit , logic , and other recursively packed arrays.

Single Dimensional Packed Arrays

A one-dimensional packed array is also called as a vector .

Multidimensional Packed Arrays

A multidimensional packed array is still a set of contiguous bits but are also segmented into smaller groups.

The code shown below declares a 2D packed array that occupies 32-bits or 4 bytes and iterates through the segments and prints its value.

Let us see a 3D packed array now.

Types, Operator, and Expressions

Like ordinary software programming languages, SystemVerilog allows designers manipulate different types and data objects when modeling the hardware. Although bears much similarity to languages such as C/C++ (in fact SystemVerilog is influenced by them), SystemVerilog is a language to model hardware, which has different semantics than software programming models. This chapter explores the type system and associated operators in SystemVerilog.

2.1 Data Types

SystemVerilog uses the terminology of data type and data objects to distinguish between objects and its data type. As specified in the language specification, a data type is a set of values and a set of operations that can be performed on those values. A data object is a named entity that has a data value and a data type associated with it.

2.1.1 4-State Values

One major distinction between SystemVerilog and other software programming languages is that the value set in SystemVerilog consists of the following four basic values:

- 0 : represents a logic zero or false condition

- 1 : represents a logic one or true condition

- x : represents an unknown value

- z : represents a high-impedance state.

Values 0 and 1 serve the same purpose as in languages such as C/C++, but x and z are hardware specific. High-impedance value z typically implies a physically disconnected state, i.e. an infinitely high resistance. It commonly appears in designs where a pin used as a bi-directional bus, e.g. tri-state. Unknown value x means the system is able to determine the value, which may happen in various condition. One common situation for x to appear in simulation is usage of uninitialized memory cells. Another common scenario is low-power designs where some part of circuit is “shut-down”, i.e. no supply voltage. Any signal coming out from the shut-down region will be x. Keep in mind that x can propagate through your circuit if not taken care of, since any logic operation on unknown values results in unknown values.

Notice that the truth table for 4-state values are slightly different than the normal 2-state values. Any 4-state value OR with 1 is 1 , any 4-state value AND with 0 is 0, and any 4-state value XOR with x is x . This can be useful when dealing with x-prorogation.

Data types that only use 0 or 1 have 2-state values.

2.1.2 Basic data types

logic is the most commonly used basic data types in SystemVerilog. logic signal has 4-state values. It can either represent a combinational signal or a sequential signal, since the downstream tools such simulator and synthesis tools will determine whether to instantiate a flip-flop based on the usage. A rule of thumb is that any signals in your synthesizable design should be declared as logic (a few exceptions apply, which will be discussed). This is to ensure that the simulator and synthesis tool agree with each other, avoiding critical bugs that can only been discovered through gate-level simulation or even post-silicon tests. For instance, if a signal is declared as 2-state value, the simulator will happily compute with 0 and 1s. However, since the actual silicon has z and x values, we will see a discrepancy after the synthesis, which leads to a potential bug.

By default, a signal declared as logic only has one bit value. To declare a multi-bit signal, we can do logic[15:0] a , which declares a 16-bit signal. Notice that we can also do logic[0:15] a . The difference is bit-ordering, similar to endianness for byte-ordering. Typically bit-ordering follows the same endianness as the byte order. It is highly recommend to use a consist bit-ordering throughout the design to avoid potential bugs. In this book we will use big-endian and high:low bit-ordering.

By default, every declared variable is unsigned. To declare a signed variable, use signed keyword such as logic signed [15:0] a . Although SystemVerilog allows you to mix signed variable with unsigned, similar to C/C++, it leaves a potential bug that cannot be caught by the compiler (some tools may produce a warning), we shall never mix signed and unsigned arithmetics and any assumption about the how the automatic conversion work is grounded for future errors that is difficult to debug.

To declare an array, we can add extra dimension to the “left”, such as logic[3:0][15:0] a , which declares 4 16-bit logics. We can adding arbitrary more dimensions as well. The array created by such approached is called packed array. To access the first 16-bit logic , we can do a[0] . Notice that we can also slice out a sub-array, such as a[1:0] , which gives as the first two values.

Notice that we can also do logic[15:0] a[3:0] , which is called unpacked array. Although unpacked array has advantage over packed array such as giving simulator more flexibility to allocate arrays since they do not need to be contiguous, because of that, we cannot slice a sub-array, nor can we bulk assign values. Again, choosing which representation depends on the project style, as long as it is consistent throughout the entire project. In this book we will use packed array.

2.1.2.1 2-state Variables

SystemVerilog also defines 2-state types, typically used for test benches or functional models that are more high-level. Unlike C, these data types has pre-defined widths, as show in Table 2 .

| Type | Bit width |

|---|---|

| bit | 1 |

| byte | 8 |

| shortint | 16 |

| int | 32 |

| longint | 64 |

2.1.3 Enumeration

SystemVerilog defines enumerations as a set of integral named constants, similar to that of C/C++. Enumeration need to be declared with a type with the default type be int . Since int is unwelcoming in synthesizable RTL, we shall always use logic data types. An example of enumeration is shown below:

Here are some rules regarding the name and integral values of enumeration:

Values in enum can be integers and increment from an initial value of 0. This, however, can be overridden, as shown below. In this case, STATE2 will be 2 and STATE3 will be 3.

- Both the enumeration names and their integer values shall be unique. This can be combined with the first rule.

The integer values in enumerate will be casted to their corresponding type. An overflow will be treated as an error

Enumeration are strongly typed. Although directly assigning integer to enumerate variables will trigger an automatic cast, we highly recommend to use explicit cast.

There are several helper functions with enumerated types:

first() : returns the value of the first member of the enumeration.

- last() : returns the value of the last member of the enumeration.

next(int unsigned N = 1) : returns N th next enumeration stating from the current value.

prev(int unsigned N = 1) : returns N th previous enumeration value starting from the current value.

Notice that next() and prev() are type-safe ways to increment enumeration values, which is highly recommend to use compared to simply addition followed by mod.

2.1.4 Struct

To represent data in a more meaningful way, SystemVerilog allows users to define a struct similar to C/C++. The members of a struct can be any data type, thus nesting struct is allowed. Since struct represents an aggregated values, similar to array, we have the concept of packed and unpacked struct. By default, without packed keyword, the struct is unpacked. Again we will use packed struct in this book. Here is an example to define an instruction type;

2.1.5 User-Defined Types

Like C, SystemVerilog allows complex data types to be aliased to a new type using the keyword typedef to make the code more readable. The syntax is similar to that of C as well:

For instance, to define the state enumeration as a new type, we can do something such as

enum definition is between typedef and state_enum_t . We can then use state_enum_t as a type to declare state variable. Notice that we add suffix _t to indicate that state_enum_t is a user-defined type. This is a useful naming convention that has been adopted in many design style guides and we will follow this convention in the book.

Similar to enum , we can use typedef to give struct a type name and re-use it later.

In the example here we first define data_t and refer to it when defining inst_t . Since we use packed for both struct , we can actually assign the instruction to a 32-bit signal.

We can also use typedef to define other types. For instance, typedef logic[7:0] byte_logic defines a byte_logic as 8-bit logic. We can stack typedef on top of each other. For instance, typedef byte_logic[7:0] int_logic defines int_logic to be a packed array of byte_logic .

2.1.6 Union

Although SystemVerilog offers the union similar to that of C/C++, it introduces a potential type loophole since the union can be updated using a value of one memory type and read as a value of another member type. To avoid this, SystemVerilog introduce a new construct called tagged union. A tagged union stores both the member values and a tag . The tag and value can only be updated together using a type-checked expression, as specified by the SystemVerilog standard. We will focus on tagged union since it offers more type safety and it is an underrated feature introduced by SystemVerilog.

In the example here, we will try to specify RISC-V basic instruction formats. The complete code can be found in 02/tagged_union.sv . Unfortunately, at the time of writing, only the latest vcs supports tagged union feature.

Notice that we use the keyword packed here, which tells the compiler to check the bit-width for each union member to make sure they are match. In most cases we want the same size, hence packed needed. However, in the case where tagged union has unmatched bit-width, the tools need to layout the memory carefully. Readers are encouraged to refer to Section 7.3.2 in the SystemVerilog standard for more details.

In the example, we have explicitly specify the tag for the variable, and the tag value is checked at runtime to ensure the type correctness.

For completeness, we cover the ordinary union here, which shares the same semantics as that of C/C++.

In this example, we can assign value to raw_value and then read out appropriate values from inst .

2.1.7 Non-Synthesizable Data Types

When modeling high-level logic designs, such as functional model used for test benches, we can use non-synthesizable data types to reduce the amount of work. For instance, SystemVerilog offers data type real and shortreal the same way as double and float in C, respectively, which conforms to IEEE Standard 754. This can be useful when developing models that needs floating point. HOwever, please keep in mind that if you want to use floating points in your synthesizable design, you have to either use vendor provided IPs, or implement your own. The former approach is recommended, since they have been thoroughly verified and optimized for various design metrics.

Another data-type non-synthesizable data type is string . string in SystemVerilog is close to that of Python where the space allocation is fixed. However, although string itself is not synthesizable, logics can be assigned directly from string literals. The tools will automatically convert the string literal into bytes based on the ASCII table behind the scene. Please keep this in mind when using string literals in your synthesizable design, as shown in the code usage in the code blow. Notice that since the string literal is represented as logic, we can display it in both string and number format, whereas the the string data type cannot.

One thing to keep in mind when using string literal assigned to numeric types such as logic : if the string length smaller than the bit width of the variable, 0 padding happens. SystemVerilog will pad 0 to the left, which can be a potential problem as normal software programming languages do not have such behavior.

2.1.7.1 Other Data Types

There are other data types in SystemVerilog we have not covered so far, such as event and chandle . We will cover chandle later in DPI, which is a data type used for foreign language pointers.

2.1.8 Type Casting

Many types in SystemVerilog are strongly typed, meaning a wrong type assignment will trigger either a compiler warning or error, such as directly assigning logic values to enum variables. Unfortunately its predecessor Verilog is weak-typed and SystemVerilog inherits all its shortcomings, such as mixing with signed and unsigned assignments. To make the code less error-prone, it is recommended to stick with explicit casting whenever there is a type mismatch, rather than relying on the language’s default type conversions.

A data type can be casted into another using the cast ' operation. The general syntax is

For instance, suppose we have a enum type state_enum_t defined earlier, and we want to directly assign a logic to it (not recommended but in some cases it is necessary), we can cast the logic variable to the enum type we want, as shown below.

To cast an unsigned number to signed, we can use signed'() , and unsigned ()` to cast signed to unsigned numbers.

2.1.9 Variable scopes and lifetime

Variables in SystemVerilog can have different lifetime depends on where and how they are defined. We will discuss more in details in the next chapter when we discuss various scopes.

2.2 Operator and Expressions

2.2.1 numeric literals.

Numeric literals in SystemVerilog can be specified in decimal, hexadecimal, octal, or binary format. The general syntax to specify a numeric literals is shown below (taken from SystemVerilog standard A.8):

By default, any numeric literal without any additional specification is in unsigned decimal base, such as 42 . To specify its size, we need ' operator to separate the size and value, such as 16'42 , which specifies a 16-bit value. We can also specify different base using letters such as d , b , and h . For instance, 16'h10 specifies a 16-bit value 0x10. If we want the numbers to be signed, we can use s after the ' , such as -16's10 , which specifies a 16-bit signed value -10. When representing non-decimal numbers, especially binary, we can use _ as a delimiter to annotate bytes. For instance, to represent 123 in a 8-bit unsigned number in binary, we can use 8'b0111_1011 , where we put _ for every 4 bits. One thing to keep in mind that although SystemVerilog allows you to drop the size, called unsized number, certain rule apply:

- The number of bits that mark up the unsized number shall lbe at least 32. This implies that if you assigned an unsized number to a variable with fewer than 32 bits, truncation will happen.

- If unsized number is used in an expression, the other values has higher number of bit width, the unsized number will be extended with respect to the highest bit, including x and z .

As a result, we only recommend to use unsized number such as 0, where the extension and truncation do not affect the actual value. For other occasions the size is recommended since it helps linters to catch size mismatch.

2.2.2 Struct and Array Literals

Although we can set the struct members individually when initializing the struct variable, SystemVerilog provides a concise way to do so. Suppose we have a struct and a variable defined as

Instead of assigning values to a and b individually, we can use the structure assignment patterns by using '{} :

This assignment pattern also works for an array of structures, which is similar to that of C++:

Array literals assignment is the same as struct literal, where each item in the array can be specified using '{} syntax. Notice that we can use replication operator {{}} to make the code more readable.

2.2.3 Operators

SystemVerilog has a rich set of operators similar to that of C/C++ with enhancement to deal with bit vectors. The complete operators and data types is listed in Table 3 , which is taken from Table 11-1 from the SystemVerilog standard.

| Operator token | Name | Operand data types |

|---|---|---|

| Binary assignment operator | Any | |

| Binary arithmetic assignment operators | Integral, real, shortreal | |

| Binary arithmetic modulus assignment operator | Integral | |

| Binary bitwise assignment operators | Integral | |

| Binary logical shift assignment operators | Integral | |

| Binary arithmetic shift assignment operators | Integral | |

| Conditional operator | Any | |

| Unary arithmetic operators | Integral, real, shortreal | |

| Unary logical negation operator | Integral | |

| Unary logical reduction operators | Integral | |

| Binary arithmetic operators | Integral, real, shortreal | |

| Binary arithmetic modulus operator | Integral | |

| Binary bitwise operators | Integral | |

| Binary logical shift operators | Integral | |

| Binary arithmetic shift operators | Integral | |

| Binary logical operators | Integral, real, shortreal | |

| Binary relational operators | Integral, real, shortreal | |

| Binary case equality operators | Any except real and shortreal | |

| Binary wildcard equality operators | Any | |

| Unary increment, decrement operators | Integral, real, shortreal | |

| Concatenation, replication operators | Integral |

Most of the operators have the same semantics as C/C++. However, there are several operators to which we need to pay attention:

- Unary logical reduction operators. This set of operators forms a reduction tree on every bit of the variable. For instance, if we have a 4-bit variable logic [3:0] a = 'b0010 . |a is equivalent to to a[0] | a[1] | a[2] | a[3] , which is 1, and &a yields 0.

- Concatenation operator {} allows multiple variable append to each other, resulting in a wider variable. Suppose we have 2 variables logic [1:0] a = 'b11 and logic [3:0] b = 'b0010 , {a, b} yields 'b110010 . We can concat as many as variable as we need. SystemVerilog also offers a shorthand to repetitively concatenate variables together. For instance, {4{'b10}} yields 'b10101010 .

- The difference between == and === lies in 4-state value comparison: == only compares 2-state and === compares 4-state. Suppose we have a = 1'bx and c = a == 1'bx , where a and c are 1-bit logic . Because == only compares 2-state, c is x . If c is defined as c = a === 1'bx , c will be 1.

- Shifter has two forms: arithmetic and logic shifters. Arithmetic shifters does signed extension when shift right where as logic shifters always pad zero when shifting. One common gotcha is that even though a variable is declared as signed, if you use >> to shift right, SystemVerilog will not perform signed extension, a behavior different from C! We have seen the actual bug went into silicon before getting caught.

Verilog Pro

SystemVerilog Arrays, Flexible and Synthesizable

In my last article on plain old Verilog Arrays , I discussed their very limited feature set. In comparison, SystemVerilog arrays have greatly expanded capabilities both for writing synthesizable RTL, and for writing non-synthesizable test benches. In this article, we’ll take a look at the synthesizable features of SystemVerilog Arrays we can use when writing design RTL.

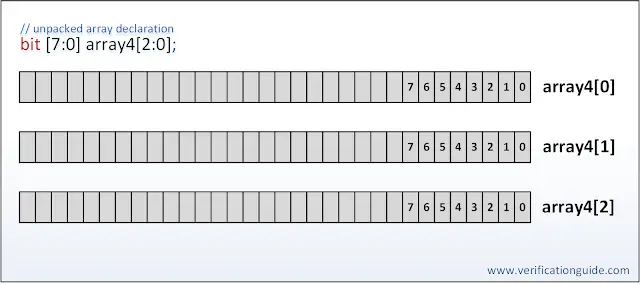

Packed vs Unpacked SystemVerilog Arrays

Verilog had only one type of array. SystemVerilog arrays can be either packed or unpacked . Packed array refers to dimensions declared after the type and before the data identifier name. Unpacked array refers to the dimensions declared after the data identifier name.

Packed Arrays

A one-dimensional packed array is also called a vector. Packed array divides a vector into subfields, which can be accessed as array elements. A packed array is guaranteed to be represented as a contiguous set of bits in simulation and synthesis.

Packed arrays can be made of only the single bit data types ( bit , logic , reg ), enumerated types, and other packed arrays and packed structures. This also means you cannot have packed arrays of integer types with predefined widths (e.g. a packed array of byte ).

Unpacked arrays

Unpacked arrays can be made of any data type. Each fixed-size dimension is represented by an address range, such as [0:1023], or a single positive number to specify the size of a fixed-size unpacked array, such as [1024]. The notation [size] is equivalent to [0:size-1].

Indexing and Slicing SystemVerilog Arrays

Verilog arrays could only be accessed one element at a time. In SystemVerilog arrays, you can also select one or more contiguous elements of an array. This is called a slice . An array slice can only apply to one dimension; other dimensions must have single index values in an expression.

Multidimensional Arrays

Multidimensional arrays can be declared with both packed and unpacked dimensions. Creating a multidimensional packed array is analogous to slicing up a continuous vector into multiple dimensions.

When an array has multiple dimensions that can be logically grouped, it is a good idea to use typedef to define the multidimensional array in stages to enhance readability. But notice the order of the dimensions become a little confusing.

SystemVerilog Array Operations

SystemVerilog arrays support many more operations than their traditional Verilog counterparts.

+: and -: Notation

When accessing a range of indices (a slice ) of a SystemVerilog array, you can specify a variable slice by using the [start+:increment width] and [start-:decrement width] notations. They are simpler than needing to calculate the exact start and end indices when selecting a variable slice. The increment/decrement width must be a constant.

Assignments, Copying, and other Operations

SystemVerilog arrays support many more operations than Verilog arrays. The following operations can be performed on both packed and unpacked arrays.

Packed Array Assignment

A SystemVerilog packed array can be assigned at once like a multi-bit vector, or also as an individual element or slice, and more.

Unpacked Array Assignment

All or multiple elements of a SystemVerilog unpacked array can be assigned at once to a list of values. The list can contain values for individual array elements, or a default value for the entire array.

This article described the two new types of SystemVerilog arrays— packed and unpacked —as well as the many new features that can be used to manipulate SystemVerilog arrays. The features described in this article are all synthesizable, so you can safely use them in SystemVerilog based RTL designs to simplify coding. In the next part of the SystemVerilog arrays article, I will discuss more usages of SystemVerilog arrays that can make your SystemVerilog design code even more efficient. Stay tuned!

- Synthesizing SystemVerilog: Busting the Myth that SystemVerilog is only for Verification

- 1888-2012 IEEE Standard for SystemVerilog

- SystemVerilog for Design Second Edition: A Guide to Using SystemVerilog for Hardware Design and Modeling

Sample Source Code

The accompany source code for this article is a toy example module and testbench that illustrates SystemVerilog array capabilities, including using an array as a port, assigning multi-dimensional arrays, and assigning slices of arrays. Download and run it to see how it works!

[lab_subscriber_download_form download_id=11].

Share this:

- Click to share on LinkedIn (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on Facebook (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

36 thoughts on “SystemVerilog Arrays, Flexible and Synthesizable”

Really nice article Jason. Makes for a great quick introduction and reference. I have personally found System Verilog arrays as one of the best ways to convert a Verilog user to System Verilog.

Chapter 5 and specifically Fig 5-5 in the System Verilog for Design book are the best: http://read.pudn.com/downloads166/sourcecode/math/758655/Springer%20-%20SystemVerilog%20for%20Design,%202nd%20Edition.pdf

I believe you have a mistake at the article. Regarding: busB = busA[7:6]; // select a 2-vector slice from busA busB = busA[6+:1]; // equivalent to busA[7:6]

but, busA[6+:1] is different from busA[7:6]! busA[6+:1] is actually busA[6:6] and: busA[6+:2] is busA[7:6]

Regards, Tomer

Hi Tomer. Yes you’re correct! I made a typo there, it’s fixed now. Thanks for spotting it!

I don’t see why we need packed/unpacked array for synthesis. FPGA is not limited with a fix size of memory like computer. The compiler should keep only what we need. Compiler will never allocate useless bits, it’s even opposite.

Same for packed and unpacked struct. What is the purpose if not only simulation speed?

Hi Alexis. If your question is why the packed versions are needed, with traditional synthesis tools you need packed arrays/structs/unions to tell the synthesis tool exactly how many bits and how you want to pack a datastructure. FPGA actually does have limited resources, and each additional (unnecessary) bit of a calculation takes up an additional lookup table. Similarly an extra bit in a calculation will require more gates in an ASIC. I wonder if part of the reason came from this desire for hardware engineers to have complete low level control of the synthesis result.

However, I think generally synthesis tools and Verilog/SystemVerilog rules are smart enough to figure out the minimum number of bits you want in a calculation. So you could argue since tools are so smart, why do we still need to specify the packing. I don’t have a good answer, but I think one day (maybe soon) you will be right and we won’t need to specify packed structures anymore.

I see, exactly since the synthesis tools removes the unused bits from the RTL. Then even if I set unpacked array, at the end, the RTL will be as if I chose packed array. Thank you and sorry for my late reply.

Hi May I confirm if there is a typo on this example typedef bit [4:0] bsix; // multiple packed dimensions with typedef bsix [9:0] v5; // equivalent to bit[4:0][9:0] v5

typedef bsix mem_type [0:3]; // array of four unpacked ‘bsix’ elements mem_type ba [0:7]; // array of eight unpacked ‘mem_type’ elements // equivalent to bit[4:0][9:0] ba [0:3][0:7]

Should the last comment be bit[4:0] ba [0:3][0:7] instead of bit[4:0][9:0] ba [0:3][0:7]?

Yes you’re right! Thanks for catching it!

Got it, thanks. By the way, if I have a 3D array, and I want to be able to slice of a 2D portion when accessing it, would you recommend to build a 3D array as “logic [HEIGHT-1:0][WIDTH-1:0] array [DEPTH]” or “logic [WIDTH-1:0] array [DEPTH][HEIGHT]”

For example, I have several submodules that expect a 2D array input, and I plan to connect them by slicing off the 3D array, so just wondering which way is preferred, “logic [HEIGHT-1:0][WIDTH-1:0] array [DEPTH]” or “logic [WIDTH-1:0] array [DEPTH][HEIGHT]”

You can slice a 2D array out of a 3D array with both ways of coding, or even “logic array [width][depth][height]”. The difference is whether you want the 2nd (middle) dimension to be packed (left of array name) or unpacked (right of array name). In your example, since each “element” is only a single bit (logic), it probably doesn’t matter which way you code it; I would actually probably code it as “logic array [width][depth][height]” to clearly show each element is only a single bit. But if you really meant a 2D array of multi-bit vector, then I would use “logic [vector_width-1:0] array [depth][height]” to show that more clearly.

The packed vs unpacked dimensions matter more if you are instead creating multi-dimensional arrays of structs or more complex data types, in which case there may be rules that the data structures must be packed (on the left) for synthesis.

Got it, thanks for sharing 🙂

1- Why do we still need to use [7:0]? We can use `busB = busA[0+:8];` and use directly the number of bits. It avoids using paraneter like `bus[PARAM-1:0]`, better to write `bus[0+=PARAM]`

2- You said `bus[6+:2]` is equivalent to `bus[7:6]` how to use big endianness to get bus[6:7]? I guess it’s not possible.

Sorry, I misread and I simulated. We can’t define logic using +:, you can delete the question.

Hi, I am writing a code in system verilog, and I wondered if there is a way to index an array from 1? Is this correct, and can I access array a from 1 to q_size?

logic a [1:q_size];

Also, unrelated question but I would be glad if you could give me an answer: I generate a queue made of number (q_size) of my blocks, which are connected with signals, so I need a number (q_size) of signals, which I intenteded to define as example above. In generate for loop I map signals to ports this way:

my_module( .my_input(a[i+1]) //i is genvar )

Is this correct, can I work with indexes this way? Thank you VERY MUCH 🙂

Hi Ivana. It is certainly possible to index an array from 1, like what you wrote. Hardware designers generally like to think and code with index starting with 0 for convenience (for example in your code you wouldn’t need a +1 if the index started at 0). Yes you can use a genvar to index into a vector. Your code should work.

Thanks for the awesome blog posts. Arrays with negative indices seem to compile (at least using the Cadence tools). What I am wondering is, do arrays with negative indices actually synthesize?

parameter integer unsigned width = 0; logic [width-1:0] x;

This compile and in SimVision I actually see x[-1:0] in waves. I am curious to know if this is a quirk in the simulator or does this actually synthesize to a two bit logic equivalent?

Thanks, Sami

Hi Sami. Another interesting question 🙂 I have never used a negative index because that goes against the coding guidelines at work, so I don’t know for sure… but I would guess it would work as expected (if your synthesis tool doesn’t complain).

I have a question about the comparison of mixed arrays that I think would fit in here:

consider the following code:

module testModule #( parameter logic [7:0] TP_A = 8’h01, parameter logic [7:0] TP_B = 8’h02, parameter logic [7:0] TP_C = 8’h03, parameter logic [7:0] TP_D = 8’h04 )( input logic clock_104, input logic reset_n, input logic [7:0] sampleData [12:0] output logic [7:0] errorCnt );

logic [7:0] comp0 [12:0]; assign comp0 = ‘{TP_A,TP_B,TP_C,TP_D,TP_A,TP_B,TP_C,TP_D,TP_A,TP_B,TP_A,TP_B,TP_C};

always @(posedge clock_104) begin if (reset_n == 1’b0) errorCnt <= '{default:0}; else begin if (sampleData == {TP_A,TP_B,TP_C,TP_D,TP_A,TP_B,TP_C,TP_D,TP_A,TP_B,TP_A,TP_B,TP_C} ) begin // this generates an error of illegal comparison to unpacked array if (sampleData == comp0 ) begin // this works fine

Why does one if statement work fine and the other one creates an error? Are they not doing the same thing?

Thank you for your help!

Hi Tom. I tried some variations of your experiment.

A pure array literal. This worked. if (sampleData == ‘{8’h00, 8’h00, 8’h00, 8’h00, 8’h00, 8’h00, 8’h00, 8’h00, 8’h00, 8’h00, 8’h00, 8’h00, 8’h00}

Add an apostrophe in front of the array: if (sampleData == ‘{TP_A,TP_B,TP_C,TP_D,TP_A,TP_B,TP_C,TP_D,TP_A,TP_B,TP_A,TP_B,TP_C} )

The simulator (VCS 2014.10) then reported the following error:

Error-[SV-IUAP] Illegal use of assignment pattern design.sv, 22 “(sampleData == ‘{TP_A, TP_B, TP_C, TP_D, TP_A, TP_B, TP_C, TP_D, TP_A, TP_B, TP_A, TP_B, TP_C})” An assignment pattern can only be used in one of the sides of an assignment-like context. Please consider rewriting it using individual array elements.

I suspect the simulator is somehow trying to do two levels of assignments in the error case, and that cannot be done within a comparison? However, I couldn’t find a statement in the LRM that explained why it is not allowed either…

That is a kind of weird. Thank you for taking the time and looking into this. I appreciate it.

is input node [6-1:0] A the same same input node [5:0] A

Hi Mike. Yes that is identical.

Hi Jason, Thank you for the wonderful forum. I have a few queries. How can I check the bit order ( MSB first and LSB last) of a packed array? e.g. input logic[7:0] test1; and output logic [7:0] out1; Would be kind to explain me.

There are several SystemVerilog system tasks that you can use to do that. See section 20.7 Array Querying Functions of the 2012 SystemVerilog LRM. Some examples are:

- $left shall return the left bound of the dimension. For a packed dimension, this is the index of the most significant element. For a queue or dynamic array dimension, $left shall return 0.

- $right shall return the right bound of the dimension. For a packed dimension, this is the index of the least significant element. For a queue or dynamic array dimension whose current size is zero, $right shall return –1.

- For a fixed-size dimension, $increment shall return 1 if $left is greater than or equal to $right and –1 if $left is less than $right. For a queue or dynamic array dimension, $increment shall return –1.

- $low shall return the same value as $left if $increment returns –1, and the same value as $right if $increment returns 1.

- $high shall return the same value as $right if $increment returns –1, and the same value as $left if $increment returns 1.

- $size shall return the number of elements in the dimension, which is equivalent to: $high – $low + 1.

Thank you Jason for your venerated inputs.

I’d like to try this, but not having much luck.. for example, I’ve created an .sv module that declares eight, 16-bit registers:

module test ( output reg [ 15 : 0 ] regTest[ 0 : 7 ] … );

Then in another .sv file, I try to instantiate like this:

wire [15:0]test[0:7]; test test_u0 ( .regTest (test) … );

However the above says an error that it cannot bind.. I’ve tried using the packed syntax, but it doesn’t seem to make any difference.. any suggestion what might be the problem?

Thanks! Ben

Hi Ben. I tried your code out on edaplayground here , and didn’t have any problem. Perhaps something else was causing the issue?

Hi want to extract only columns in packed 2-D array, for eg logic [255:0][299:0] array1 has 256 rows each having 300 bits ; if I wanted to extract 1st column through array slicing operation how do I do it? Like array1[0] gives first row array1[1] gives second row etc ; Thanks a lot

Hi Venkat. The array definition makes extracting one dimension easier than the other, so you should be careful about how you define the array. To accomplish what you want to do, you can write a loop to extract each element that you need and assign that element to a new 256-entry single dimensional array.

Can I include an unpacked array in a struct or an interface? For example, I like to pass an FIFO and some other info of a module to another to snooping. can I have a struct like this: typedef struct packed { logic [5:0] dev_sel; logic [31:0] wr_pending_fifo_dv; logic [31:0] wr_pending_fifo_mem [128]; } dev_wr_fifo_s;

Would an interface have the same elements?

Thanks Agnes

Hi Agnes. If you create an unpacked struct (typedef struct, without the packed keyword), then you can have an unpacked array like the wr_pending_fifo_mem in the structure. However, Design Compiler will not synthesize an unpacked struct. What are you trying to achieve? Putting a FIFO into a struct seems to be a bit of a strange construct.

Always thanks to your post. Again, I hope to ask clarify below comment. /////////////////////////////////////////////////////////////////////////// bit [3:0] [7:0] joe [0:9] // 10 elements of 4 8-bit bytes // (each element packed into 32 bits) typedef bit [4:0] bsix; // multiple packed dimensions with typedef bsix [9:0] v5; // equivalent to bit[4:0][9:0] v5 typedef bsix mem_type [0:3]; // array of four unpacked ‘bsix’ elements mem_type ba [0:7]; // array of eight unpacked ‘mem_type’ elements // equivalent to bit[4:0] ba [0:3][0:7] – thanks Dennis! /////////////////////////////////////////////////////////////////////////// Considering its semantic, I think it needs to be fixed as below. In my previous experience, I was also confused for that. 1. equivalent to bit[4:0][9:0] v5 => equivalent to bit[9:0][4:0] v5 2. equivalent to bit[4:0] ba [0:3][0:7] => equivalent to bit[4:0] ba [0:7][0:3]

Hi Yunsung. I just ran a test to prove it to myself. You’re right! Thanks for correcting this major mistake!

Is accessing to array slices with dynamic indexing but fixed width synthesizable? For example:

// input_byte is a 8 bit logic input // input_index is 3 bit logic input localparam int unsigned FIXED_WIDTH = 8; logic[63:0] data_array; data_array[input_index *FIXED_WIDTH +: FIXED_WIDTH] <= input_byte;

Hi Veli. I think that should be synthesizable. I have written similar code where the LHS is a dynamic index to an array. I have not additionally used a fixed width slice, but I think since the width is a fixed parameter, it shouldn’t be a problem. A dynamic index and a dynamic width, I think would be a problem.

Leave a Comment Cancel reply

Notify me of follow-up comments by email.

Notify me of new posts by email.

This site uses Akismet to reduce spam. Learn how your comment data is processed .

Verification Guide

Packed and Unpacked array

Packed and unpacked array in systemverilog.

Table of Contents

- The term packed array is used to refer to the dimensions declared before the data identifier name

- The term unpacked array is used to refer to the dimensions declared after the data identifier name

Packed array

- Packed arrays can be of single bit data types (reg, logic, bit), enumerated types, and recursively packed arrays and packed structures

- Vector: A vector is a multi-bit data object of reg/logic/bit declared by specifying a range

- Scalar: Scalar is 1-bit data object of reg/logic/bit declared without specifying a range

- A packed array is a mechanism for subdividing a vector into sub-fields, which can be conveniently accessed as array elements.

- A packed array is guaranteed to be represented as a contiguous set of bits.

Packed array example

The below diagram shows storing packed array as a contiguous set of bits.

UnPacked array

- Unpacked arrays can be of any data type.

- Unpacked arrays shall be declared by specifying the element ranges after the identifier name.

- An unpacked array may or may not be so represented as a contiguous set of bits.

Unpacked array example

Below diagram shows storing unpacked array as a non-contiguous set of bits.

❮ Previous Next ❯

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile .

- Intel Community

- Product Support Forums

- Intel® Quartus® Prime Software

SystemVerilog structure or struct assignment by keyword.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Printer Friendly Page

- Mark as New

- Report Inappropriate Content

- systemverilog

- All forum topics

- Previous topic

Link Copied

Community support is provided during standard business hours (Monday to Friday 7AM - 5PM PST). Other contact methods are available here .

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice .

- ©Intel Corporation

- Terms of Use

- *Trademarks

- Supply Chain Transparency

- Stack Overflow for Teams Where developers & technologists share private knowledge with coworkers

- Advertising & Talent Reach devs & technologists worldwide about your product, service or employer brand

- OverflowAI GenAI features for Teams

- OverflowAPI Train & fine-tune LLMs

- Labs The future of collective knowledge sharing

- About the company Visit the blog

Collectives™ on Stack Overflow

Find centralized, trusted content and collaborate around the technologies you use most.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Get early access and see previews of new features.

Analyze a packed structure in SystemVerilog to determine it's size?

In SystemVerilog is there a way to analyze a packed structure and determine it's overall size in bits?

For example, I would like to be able to determine programmatic-ally that the size of the above structure is 45.

I've looked at the "Aggregate data types" section (Chapter 7) of the IEEE 1800-2012 SystemVerilog Language Reference Manual , and didn't see anything like this.

Is this possible? If so, how?

- system-verilog

- 1 Related Answer – Morgan Commented Mar 14, 2014 at 17:46

Use $bits() from IEEE 1800-2012 § 20.6.2 Expression size system function :

The $bits system function returns the number of bits required to hold an expression as a bit stream.

Direct example from the LRM :

... Given the declaration: typedef struct { logic valid; bit [8:1] data; } MyType; the expression $bits(MyType) shall return 9, the number of data bits needed by a variable of type MyType.

Your Answer

Reminder: Answers generated by artificial intelligence tools are not allowed on Stack Overflow. Learn more

Sign up or log in

Post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged verilog system-verilog or ask your own question .

- The Overflow Blog

- How to build open source apps in a highly regulated industry

- Community Products Roadmap Update, July 2024

- Featured on Meta

- We spent a sprint addressing your requests — here’s how it went

- Upcoming initiatives on Stack Overflow and across the Stack Exchange network...

- Policy: Generative AI (e.g., ChatGPT) is banned

- The [lib] tag is being burninated

- What makes a homepage useful for logged-in users

Hot Network Questions

- I can't mount my external hard drive in Linux

- How soon should you apply and unapply the sustain pedal after markings?

- Will electrolysis hydrolyze esters?

- Position where last x halfmoves are determined

- Travel to Mexico from India, do I need to pay a fee?

- Does concentrating on a different spell end a concentration spell?

- Is there any other reason to stockpile minerals aside preparing for war?

- Remove duplicates in file (without sorting!) leaving the _last_ of the occurences

- Does the Ogre-Faced Spider regenerate part of its eyes daily?

- What’s the highest salary the greedy king can arrange for himself?

- What are these courtesy names and given names? - confusion in translation

- Cryptography elements requested for a plot in a story

- Is it possible to complete a Phd on your own?

- Line from Song KÄMPFERHERZ

- Contains floating input pins

- Geometry question about a six-pack of beer

- How well does the following argument work as a counter towards unfalsifiable supernatural claims?

- Why can't LaTeX (seem to?) Support Arbitrary Text Sizes?

- Could someone translate & explain the Mesorah?

- Is it prohibited to consume things that unclean animals produce?

- What is the impact on an index when I am widening a key varchar column

- Ideal diode in parallel with resistor and voltage source

- Why would a plane be allowed to fly to LAX but not Maui?

- Phantom points in QGIS do not dissapear

An Introduction to SystemVerilog Arrays

This post of the the first of two which talk about SystemVerilog arrays . In this post, we will talk about static arrays , array assignment , loops and packed vs unpacked arrays .

In SystemVerilog, we can write arrays which have either a fixed number of elements or a variable number of elements.

Fixed size arrays are also known as static arrays in SystemVerilog. When we declare a static array, a fixed amount of memory is allocated to the array at compile time . As a result of this, we can't add new elements or resize the array during simulation.

In contrast, we can allocate extra memory or resize a dynamic array while a simulation is running.

Static arrays are generally simpler to use than dynamic arrays and are similar to verilog arrays . Therefore, we will discuss static arrays in more depth in the rest of this post.

In the next post in this series, we will talk about more advanced SystemVerilog arrays. This includes a discussion of dynamic arrays , queues and associative arrays .

Static Arrays in SystemVerilog

Static arrays are the simplest form of array to work with in SystemVerilog. We use static arrays in exactly the same way as we would use an array in verilog .

The code snippet below shows the general syntax which we use to declare a static array in SystemVerilog.

In this construct, we use the <elements> field to declare how many elements are in our array.

In contrast to verilog, we can use a single number in the <elements> field to determine how many elements are in the array.

When we use this approach, SystemVerilog creates a zero indexed array as this is the most commonly used type of array. This approach is also consistent with the way that arrays in C are declared and created.

However, we can also use the old verilog syntax to specify a value for the low and high indexes in our array. When we use this approach, the <elements> field takes the form [high_index : low_index].

We previously discussed the rest of the fields used in this declaration in the post on SystemVerilog Data Types .

To show how we would declare a SystemVerilog array using both approaches, let's consider a simple example. In this example, we will create an array of 4 bit logic types and we want to have a total of 16 elements.

The SystemVerilog code below shows the two different methods we could use to create this array.

- Array Assignment and Literals

After we have created an array in our SystemVerilog code, we can access individual elements in the array using square brackets.

For example, if we wanted to assign some data to the first element in an array then we would use the syntax shown in the code snippet below.

We use this same syntax to access array elements in verilog.

However, we can also use array literals to assignment data to arrays in SystemVerilog. Array literals provide us with a quick and convenient method to assign values to multiple elements in the array at the same time.

The code snippet below shows the general syntax we use to assign data to an array using an array literal.

We use the <values> field in the above code snippet to assign a value to every element in the array.

We can use three different methods to assign data to the <values> field in this construct. The most common method is to use a comma separated list of values.

The SystemVerilog code below shows how we would assign elements to an array using this technique. We can also simulate this code on eda playground .

In addition to this method, we can also use other techniques to assign the same value to multiple elements in the array.

We actually have two methods which we can use for this. Both of these methods are more concise than writing a comma separated list with duplicated values.

The first approach is to use another pair of curly braces inside the list which shows the value we want to assign. We can then put a number in front of the braces to indicate how many consecutive elements should be assigned this value.

As an example, we might want to create an array and assign all of the elements to 0. The code snippet below shows how we would do this using array literals. This code can also be simulated on eda playground .

In addition to this, we can also use the SystemVerilog default keyword inside our array literal.

We more typically use the default keyword inside of SystemVerilog struct types which we will talk about in a future post.

However, we can also use the default keyword as a convenient way to assign the same value to every element in a static array. We can't use this technique with dynamic arrays though.

As an example, we might want to create an array and assign all of the elements to 0. The code snippet below shows how we would do this using the default keyword. We can also simulate this code on eda playground .

When we work with arrays in SystemVerilog it is possible that we may try to assign data to an array element which is out of bounds . When we are working with static arrays, any attempt to do this is simply ignored.

Array Loops

When we work with arrays in any programming language, one common operation is iterating over every element in the array.

There are actually two different methods which we can use to do this in SystemVerilog.

In both case, we make use of a SystemVerilog loops . There are several types of loop which we can use in SystemVerilog and we discuss this in more detail in a later post.

However, let's take a look at both of the methods we can use to iterate over an array in more detail.

- The for loop

The first method makes use of the SystemVerilog for loop which we discuss in more depth in a later post.

The code snippet below shows the general syntax which we use to implement a for loop in SystemVerilog. This syntax is exactly the same as we use in verilog for loops .

We use the <initial_condition> field to set the initial value of our loop variable .

The <stop_condition> field is a conditional statement which determines how many times the loop runs. The for loop will continue to execute until this field evaluates as false.

The <increment> field determines how the loop variable is updated in every iteration of the loop.

We can use the for loop to generate the index for every element in an array. We can then use the loop variable to access each of the elements in the array in turn.

The code snippet below shows how we would do this in SystemVerilog. This example can also be simulated on eda playground .

In this example, we initialize the loop variable (i) to 0 in order to get the lower index of the array. We then use the $size macro to get the index of the final element in our array.

The $size macro is a built in function in SystemVerilog which returns the number of elements in an array.

Finally, we use the SystemVerilog increment operator to increment the value of the loop variable by one on every iteration. As we can see for this example, we can use C style increment and decrement operators in our SystemVerilog code.

From this we can see how the loop variable i is increased fro 0 to 7 in the for loop. This allows us to access each of the array elements in turn by using the loop variable as an index.

- The foreach Loop

The second method which we can use to loop over an array in SystemVerilog is the foreach loop.

This is a new type of loop which was introduced as a part of the SystemVerilog language. The foreach loop is designed to provide a more concise way of looping over an array.

The code snippet below shows the general syntax for the foreach loop.

In this construct, we use the <array_name> field is select the array which we want to loop over.

The <iterator> field is then automatically incremented from the low index to the high index of the selected array.

We can use the <iterator> field in the body of our foreach loop in the same way as we used the loop variable in the body of the for loop.

As we can see, we don't need to manage the array index when we use the foreach loop. As a result of this, we generally find that the foreach loop is easier to use than the for loop.

To demonstrate how we would use the foreach loop, let's rewrite the example from the section on for loops.

In this example, we created an array of 8 elements and then looped over each element in turn.

The code snippet below shows how we would implement this functionality with a foreach loop. We can also simulate this example on eda playground .

As we can see from this example, when we use a foreach loop we generally have to write less code to achieve the same result.

Multi Dimensional Arrays in SystemVerilog

So far, all of the arrays which we have discussed in this post have been one dimensional.

However, we can also create SystemVerilog arrays which have more than dimension. To do this, we simply add another field to the end of the array declaration.

The code snippet below shows the general syntax we would use to create a 2D array in SystemVerilog.

Both of the <elements> fields in this construct take the same form as the <element> field which we previously discussed in the section on static arrays.

As a result, we can either use a single number to determine the number of elements or we can specify a value for the low and high indexes. When we use the second approach, the <elements> field takes the form [high_index : low_index].

We can add as many <element> fields as needed to create a multidimensional array. For example, if we need a 3D array, then we would use a total of 3 <element> fields in our declaration.

In order to better demonstrate how we use multidimensional arrays in SystemVerilog, let's consider a basic example.

For this example, let's say that we want to create an array which has 2 elements both of which contain 4 8-bit wide logic types.

To do this, we simply need to add an extra field to the end of our normal array declaration. The code snippet below shows how we would do this.

- Assigning Data to Multidimensional Arrays

We use the same method to assign a multidimensional array as we would for a 1D array. However, we now use a pair of square brackets to define the element in both dimensions of the array.

As an example, suppose we want to assign the value of AAh to the the last element in both dimensions of the example array we declared in the previous section. The SystemVerilog code below shows how we would do this.

We can also use arrays literals to assign data to multidimensional arrays in SystemVerilog.

However, we now have to create a literal which itself contains a separate array literal for each dimension of the array.

For example, if we have a 2D array then we would create an array literal which is made up of 2 further array literals.

As an example, let's consider the case where we want to populate both elements of the 2D array example we created in the previous section.

However, we want all elements of the first dimension to be set to 0xFF and all elements in the second dimension to be set to 0.

The code snippet below shows how we would create an array literal to populate the entire 2D array with the required data. This code can also be simulated on eda playground .

- Packed and Unpacked Arrays in SystemVerilog

In all of the examples which we have considered so far, we have used unpacked arrays.

This means that each of the elements in the array is stored in a different memory location during simulation.

For example, suppose we have an array which consists of 4 8-bit elements. The code snippet below shows how we would create this is SystemVerilog.

As most simulators use 32 bit wide memory locations, we would end up with the memory contents shown below during simulation.

As we can see from this example, unpacked arrays can result in inefficient usage of memory as parts of the memory are unused.

In SystemVerilog, we can also use packed arrays to store our data in. Packed arrays will result in more efficient usage of memory when we run our simulations in some instances.

In contrast to unpacked arrays, all elements of a packed array are stored continuously in memory. This means that more than one element can be stored in a single memory location.

The code snippet below shows the general sytnax we use to declare a packed array in SystemVerilog.

All of the fields in the packed array declaration are the same as in the unpacked declaration. In fact, the only difference is that the <elements> field now comes before the <variable_name> field rather than after it.

To demonstrate how packed arrays are different to unpacked arrays, let's consider a simple example.

For this example, we will again create an array of 4 8-bit elements. However, this time we will declare the array as a packed type array.

The SystemVerilog code below shows would we declare this packed array.

This example would result in the memory allocation shown below.

We can see from this that the packed array has used a single 32-bit wide memory location to store the entire contents of the array.

In comparison to the unpacked array example, we can see how the packed array uses less memory by packing all of the data into a single memory location in this instance.

What is the difference between static arrays and dynamic arrays in SystemVerilog?

Static arrays have a fixed number of elements which are determined at compile time. In contrast, dynamic arrays don't have a fixed sized and we can add or remove elements during simulation.

Write the code to create an array which consists of 4 8-bit elements. Use an array literal to assign all of the elements in the array to 0.

Write a foreach loop for the array which you created in the last exercise

Write the code to declare a 2D array of int types. The array should have 2 elements in the first dimension and 8 elements in the second dimension.

What is the difference between an unpacked array and a packed array?

Each element of an unpacked array is stored in an individual memory address. In contrast, packed arrays are stored continuously in memory meaning that several elements can be stored in a single memory address.

2 comments on “An Introduction to SystemVerilog Arrays”

logic [7:0] [3:0] example; will give 8 nibbles

I think you need logic [3:0] [7:0] example; for your example

Thanks for pointing out the typo, I have now corrected it.

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Table of Contents

Sign up free for exclusive content.

Don't Miss Out

We are about to launch exclusive video content. Sign up to hear about it first.

IMAGES

VIDEO

COMMENTS

SystemVerilog Structure. A structure can contain elements of different data types which can be referenced as a whole or individually by their names. This is quite different from arrays where the elements are of the same data-type. // Normal arrays -> a collection of variables of same data type. int array [10]; // all elements are of int type.

This is an example for illustration. In SystemVerilog, it has array assignment pattern and struct assignment pattern syntax. No matter the union construct here is packed or unpacked, whether it is synthesizable or not, is it a valid usage for assignment pattern?

Only packed data types and integer data types are allowed in a packed struct. Because it is defined as a vector, the entire structure can also be used as a whole with arithmetic and logical operators. An unpacked SystemVerilog struct, on the other hand, does not define a packing of the data types. It is tool-dependent how the structure is ...

Packed data always goes from MSB to LSB in field declaration order. If you declare. mem_pkt pkt; Then pkt.addr[7] corresponds to pkt[39] and pkt.addr[0] corresponds to pkt[32].pkt.data[0] corresponds to pkt[0]. Verilog is a weakly typed language and there is no way prevent assignments from packed arrays and structs to one another without some kind of linting tool.

Similar to a packed array, if memory allocated for variables in a structure is contiguous, then it is called a packed structure. Only packed data types are allowed in packed structures. Ex. A string is not a packed data type, so code will not compile. To use string as a data type in structure, unpack structures can be used. The "packed ...

SystemVerilog Struct The SystemVerilog struct groups the data types of multiple types. The entire group can be referenced as a whole, or the individual data type can be referenced by name. Struct Syntax Struct is defined with the Struct keyword followed by variables of multiple data type with in the curly braces. typedef struct packed … Continue reading "SystemVerilog Struct"

The type of the elements in an unpacked structure or array shall be valid for a packed representation in order to be cast to any other type, whether packed or unpacked. Thank you, in advance, for your cooperation. vec_pack = 320' ( vec_unpack) ; // note ()'s instead of {}'s. works for me, although it does not match the functionality of your ...

One way to define complex structs can be explained with an example. Lets be the following struct, which is a struct of integer arrays and a sub-struct called: AXI_PRM_STRCT

A packed array is used to refer to dimensions declared before the variable name. bit [3:0] data; // Packed array or vector logic queue [9:0]; // Unpacked array A packed array is guaranteed to be represented as a contiguous set of bits. They can be made of only the single bit data types like bit, logic, and other recursively packed arrays.

In the example here we first define data_t and refer to it when defining inst_t.Since we use packed for both struct, we can actually assign the instruction to a 32-bit signal.. We can also use typedef to define other types. For instance, typedef logic[7:0] byte_logic defines a byte_logic as 8-bit logic. We can stack typedef on top of each other. For instance, typedef byte_logic[7:0] int_logic ...

Packed arrays have an object name which comes after the size declaration. For example: where a is a 28-bit vector subdivided into 3 7-bit subfields. Unpacked arrays have an object name which comes before the size declaration. For example: where b is a 3-bit wide vector. Packed arrays make memory whereas Unpacked don't.

00:00 Intro00:08 struct00:56 typedef and struct01:13 with struct vs without struct02:35 formatter for struct %p03:03 unpacked and packed struct

Defining the struct. typedef struct packed { logic [17-1:0] instr; logic [10-1:0] addr; } instr_packet_s; ... When synthesizing a top-level module that takes in system verilog structus, quartus expands the structure and increases the number of parameters to the module; expanding out the struct. ...

Packed Array Assignment. A SystemVerilog packed array can be assigned at once like a multi-bit vector, or also as an individual element or slice, and more. ... with traditional synthesis tools you need packed arrays/structs/unions to tell the synthesis tool exactly how many bits and how you want to pack a datastructure. FPGA actually does have ...

Packed array. Packed arrays can be of single bit data types (reg, logic, bit), enumerated types, and recursively packed arrays and packed structures. One dimensional packed array is referred to as a vector. Vector: A vector is a multi-bit data object of reg/logic/bit declared by specifying a range. Scalar: Scalar is 1-bit data object of reg ...

case0 is an assignment pattern of 3 operands to an array of three elements. case1 is illegal because Your assignment pattern only has three (repeated) operands where nine are required. And the three operands you do have are not assignment compatible: each element. needs to be an int, not an array of ints.

Description I would like to assign values to a packed structure using keywords (e.g. code snippet below) but have run into the an apparent syntax. Browse . Community; About; ... SystemVerilog structure or struct assignment by keyword. 16704 Discussions. SystemVerilog structure or struct assignment by keyword. Subscribe More actions.

which will print it as an assignment pattern, but you will not be able choose the fields or their ordering, or apply any other individual formating. %p is good for quick and easy displays, but most people eventually wind up writing a method to format it exactly the way they want it. ... Unpacking system verilog packed struct in DPI-C call. Hot ...

enumeration-datatype, packed, SystemVerilog. ThomasKruse November 5, 2021, 4:35pm 1. Hi all, I have few questions about enumerations in packed data: According to the LRM, "only packed data types and the integer data types summarized in Table 6-8 (see 6.11) shall be legal in packed structures.". This means, no enumeration types are allowed ...

typedef struct packed unsigned {. logic [15:0] field_1; logic [7:0] field_2; logic [15:0] field_3; logic [4:0] field_4; } my_struct; For example, I would like to be able to determine programmatic-ally that the size of the above structure is 45. I've looked at the "Aggregate data types" section (Chapter 7) of the IEEE 1800-2012 SystemVerilog ...

An Introduction to SystemVerilog Arrays. This post of the the first of two which talk about SystemVerilog arrays. In this post, we will talk about static arrays, array assignment, loops and packed vs unpacked arrays. In SystemVerilog, we can write arrays which have either a fixed number of elements or a variable number of elements.